反激式电源EMI电磁干扰的系统化优化:Frenetic磁性元件仿真与实测验证

在新能源电源、工业电源与消费电子领域,功率密度持续提升、电磁兼容(EMC)标准不断趋严,传统“堆滤波器”的电磁干扰(EMI)整改方式正面临成本与空间的双重压力。为什么反激式电源在效率达标后,仍频繁卡在EMC测试环节?共模干扰的真正传播路径在哪里?是否可以在不增加滤波器体积的情况下,实现显著降噪?

在产业升级与产品轻量化趋势下,EMI问题已不只是“测试整改”,而是设计逻辑的转变。基于Frenetic在磁性仿真与结构优化方面的实战经验,本文将系统解析反激式电源EMI的源头机理与工程化解决路径。

先定位:反激EMI的两大核心噪声源

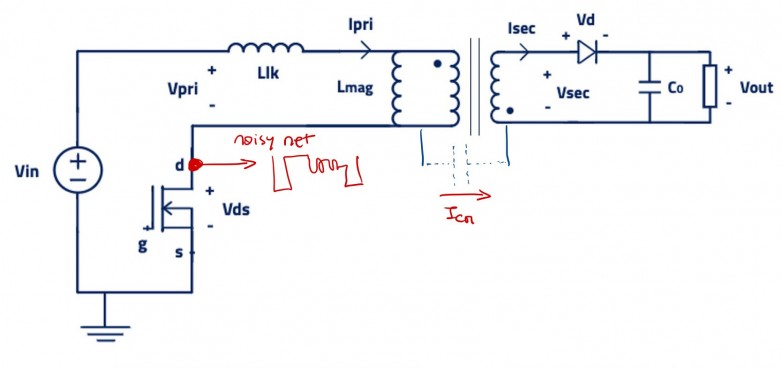

开关电源的EMI噪声,根源在于快速变化的电压和电流。反激电路中,这两个噪声源必须重点关注:

高电压变化率(dV/dt)冲击点

变压器与晶体管之间的节点是噪声重灾区!晶体管的高速开关会导致电压骤变,产生大量高频噪声,这些噪声会通过初、次级间的寄生电容串扰传播,形成共模干扰。

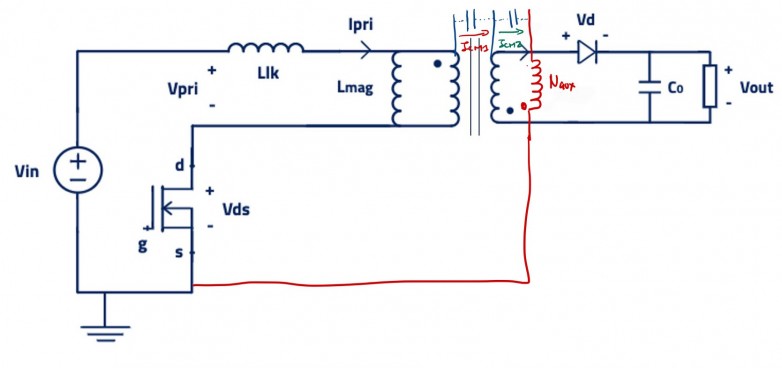

反激式变换器原理图。标注了噪声网络和绕组内电容。

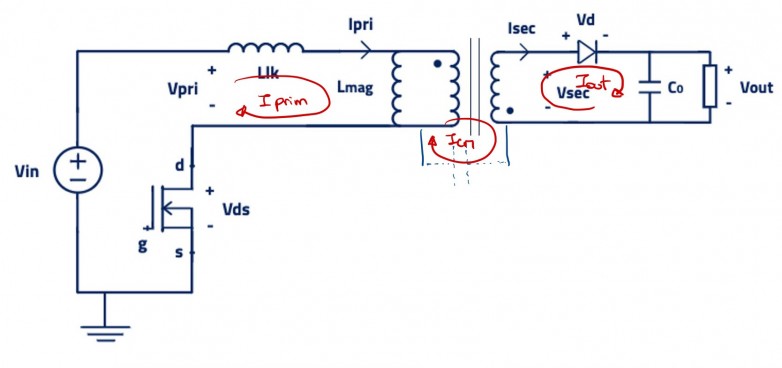

高电流变化率(dI/dt)电流环路

反激电路中有三处会出现快速变化的电流,这些环路本身就像“电磁辐射天线”。优化的核心很直接:减小印刷电路板(PCB)布局中焊盘的间距,通过缩短环路面积抑制噪声辐射。

本文将重点聚焦高dV/dt噪声——这是反激EMI的主要来源,而变压器的构造设计,直接决定了噪声抑制的效果上限。

反激式变换器原理图。标注了产生电磁干扰的电流环路。

核心方案:两种变压器技术,从源头阻断噪声

降低反激EMI的核心逻辑是:减小初、次级绕组间的寄生电容,切断共模电流(Icm)的传播路径。以下两种技术经工程验证,实操性强、效果显著:

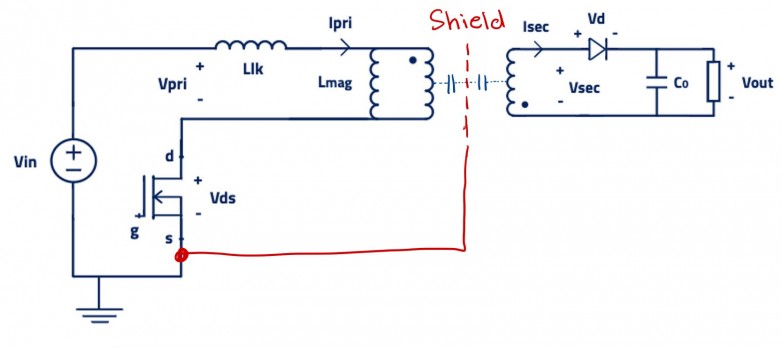

1、变压器屏蔽层:给噪声找“低阻路径”

工作原理:在初、次级绕组之间加入一层薄铜箔屏蔽层,为共模电流提供专属接地通道。噪声会优先通过低阻抗的屏蔽层入地,而非通过绕组间电容串扰到次级,从而减少干扰传播。

关键设计要点:

屏蔽层需尽可能薄,避免产生过大涡流损耗;

单端连接到本地初级接地(或其他安静接地);

若采用交错绕组设计,需设置多个屏蔽层;

铜箔不可闭环,防止形成额外干扰环路。

核心优势:工艺简单、成本可控,是量产产品的优先选择。

带屏蔽层的反激式原理图

2、抵消绕组:让噪声“相互抵消”

工作原理:在变压器中增加辅助抵消绕组,通过精准调整匝数设定其极性,使其产生与原共模电流极性相反的“抵消电流”。两者相互作用,最终让输出端的共模电流净流量趋近于零。

进阶优化:可将抵消绕组连接到辅助接地而非初级接地,实现共模平衡;也可与屏蔽层搭配使用,进一步提升降噪效果。

注意事项:制造工艺相对复杂,需通过仿真工具优化匝数和极性参数,避免引入额外损耗。

带辅助抵消绕组的反激式原理图

TI实测验证:20dB降噪不是空谈

理论是否可靠?德州仪器(TI)的65W反激转换器实测案例给出了明确答案:

测试条件

拓扑:反激式转换器

输入:通用230VAC输入,输出19.5V

变压器:匝数比5,采用“屏蔽层+辅助抵消绕组”复合设计

基准规格:基于UCC28630EVM572

测试结果对比

20dB的降噪效果意味着什么?不仅能让产品轻松通过EMC测试,还能大幅减小输入滤波器的体积和成本,为功率密度优化腾出更多空间。

关键平衡:漏感(Llk)与效率的博弈

在降噪设计中,不能忽视漏感对电源效率的影响。TI案例中做了一组对比实验:

一款变压器增加14层胶带,漏感显著提升;

另一款同结构变压器去掉这14层胶带,漏感相应降低。

实测结果显示:漏感提升会导致电源效率明显下降,而漏感的大小,直接受绕组排布和屏蔽策略的影响。

效率优化原则:

采用“初级分层绕法”,增强初、次级绕组耦合,减小漏感;

设计屏蔽层和抵消绕组时,需兼顾绕组耦合效率,避免过度牺牲漏感性能;

降低交流电阻(Rac),减少额外损耗,助力效率提升。

工程师实操设计指南

1. 量产产品优先采用屏蔽层技术,兼顾效果与成本;

2. 高EMI要求场景,可采用“屏蔽层+抵消绕组”复合方案;

3. PCB布局配合:减小高dI/dt电流环路的面积,优化接地路径,避免噪声叠加;

4. 仿真先行:使用Frenetic等专业工具,验证漏感、绕组电容等参数,减少实物试错;

5. 安规合规:输入端Y电容的选型需符合相关标准,控制漏电流风险。

核心结论

反激EMI抑制的关键,在于“精准定位+源头阻断”:找准高dV/dt、高dI/dt两大噪声源,通过屏蔽层或抵消绕组技术切断共模电流传播路径,即可实现20dB的显著降噪。同时,需平衡漏感与效率的关系,通过优化绕组排布提升耦合效率,才能实现“低EMI+高效率+低成本”的设计目标。

你在反激电源设计中遇到过哪些EMI棘手问题?欢迎访问Frenetic中文官方网站,获取更多技术资料与工程案例支持。

特别提醒:如果文章内容、图片、视频出现侵权问题,请与本站联系撤下相关作品。

风险提示:纵横网呈现的所有信息仅作为学习分享,不构成投资建议,一切投资操作信息不能作为投资依据。本网站所报道的文章资料、图片、数据等信息来源于互联网,仅供参考使用,相关侵权责任由信息来源第三方承担。

本文地址: